Product Summary

The LH52B256-70LL is a kind of high-density 262,144 bit static RAM organized as 32k x 8. The RAM is fully static in operation. An efficient design is obtained with a CMOS periphery and a matrix constructed with polysilicon load memory cells. High frequency design techniques should be employed to obtain the best performance from this device. Solid, low-impedance power and ground planes, with high-frequency decoupling capacitors, are recommended. Series termination of the inputs should be considered when transmission line effects occur.

Parametrics

Absolute maximum ratings: (1)supply voltage, VCC: -0.5 to +7.0 V; (2)input voltage, VIN: -0.5 to VCC+0.5 V; (3)operating temperature, Topr: 0 to +70℃; (4)storage temperature, Tstg: -65 to +150℃.

Features

Features: (1)access time: 70 ns; (2)automatic power down during long read cycles; (3)low-power standby when deselected ; (4)TTL compatible I/O; (5)single +5 V power supply; (6)fully-static operation; (7)package: 28-pin, 600-mil DIP; 28-pin, 300-mil SK-DIP; 28-pin, 450-mil SOP; 28-pin, 8x13 mm2 TSOP (type I).

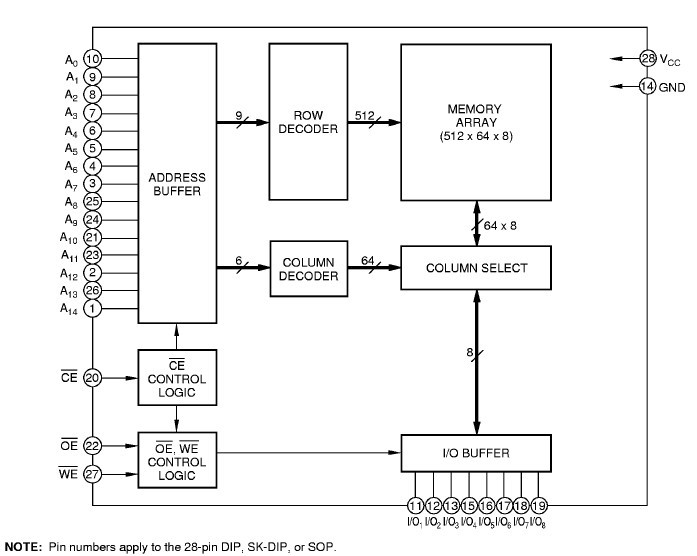

Diagrams

|

LH521028 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

LH521028A |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

LH52256 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

LH52256C |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

LH52256C-70LL |

|

IC SRAM 256KBIT 70NS 28DIP |

Data Sheet |

Negotiable |

|

||||

|

LH52256CH |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))